Floating Point Matrix Multiplication Verilog Code

Floating point multiply using verilog Jump to solution. Multiply by 2 repeatedly until it has no more decimal component.

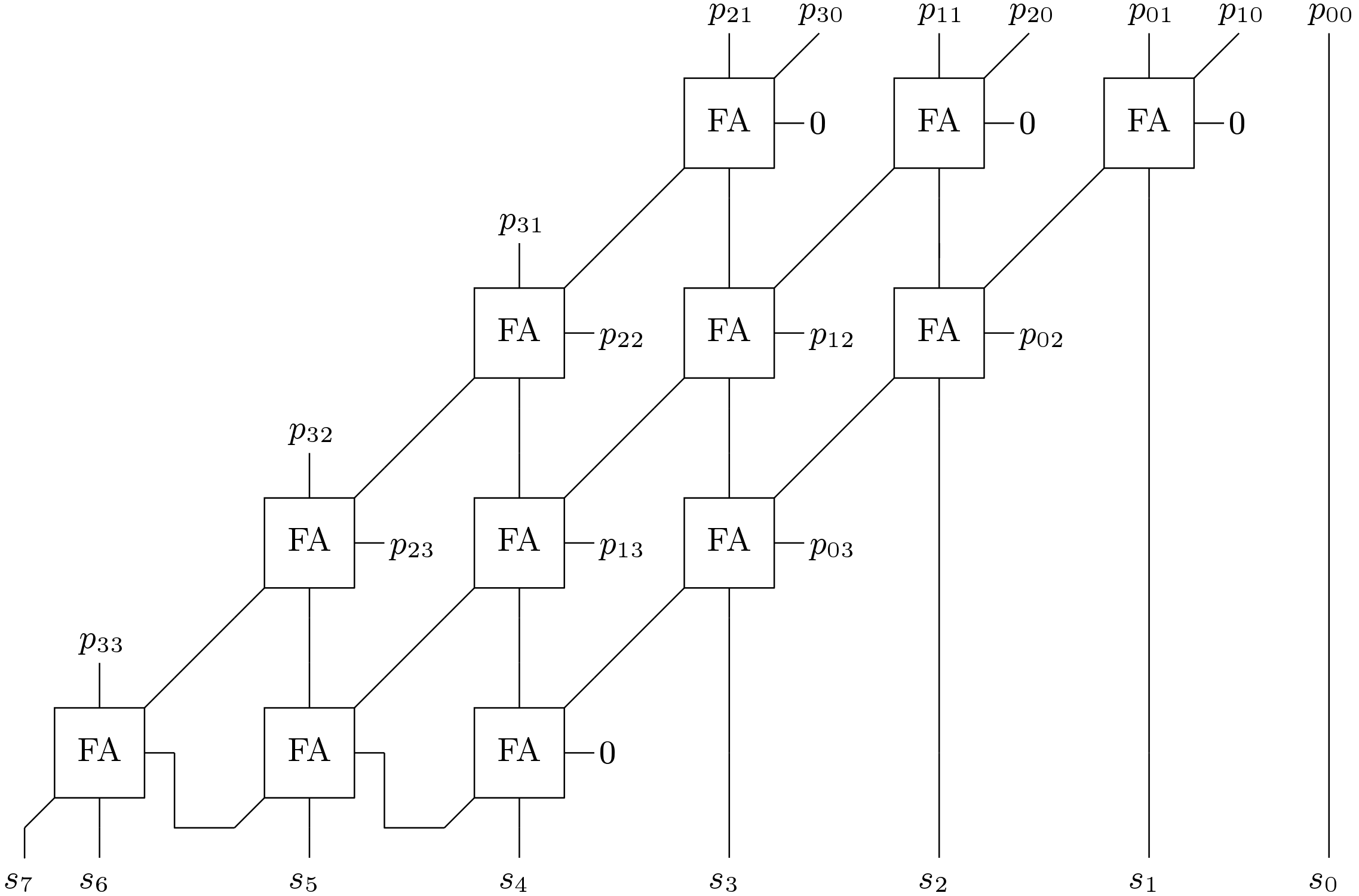

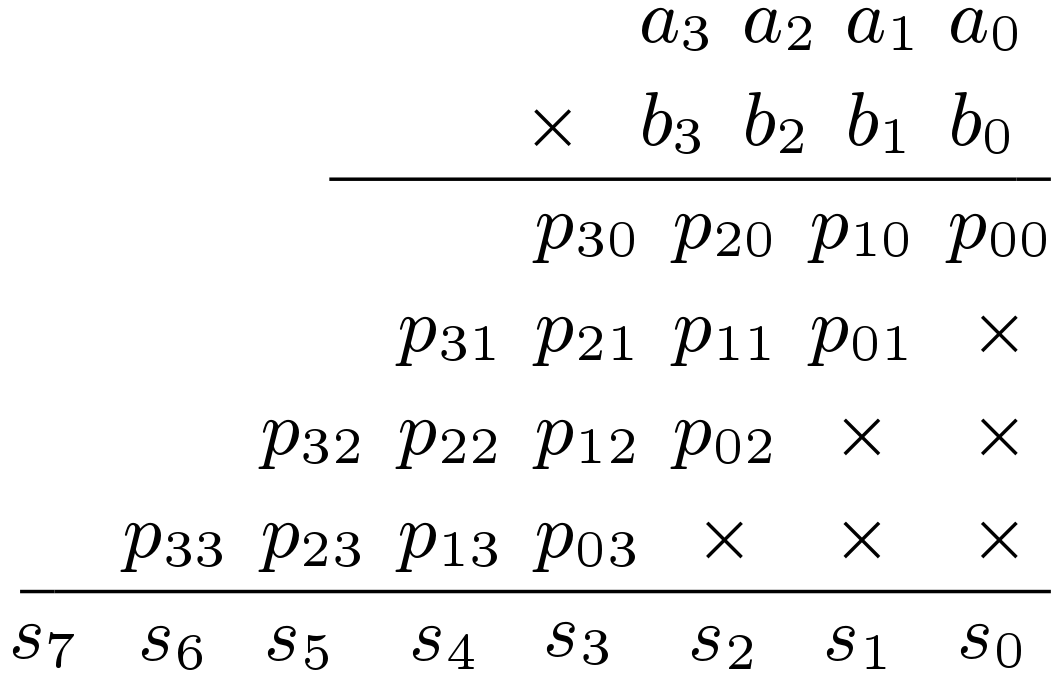

Unsigned Array Multiplier Digital System Design

Ib T sum 0.

Floating point matrix multiplication verilog code. Are designed using verilog hdl the floating point matrix multiplication accelerator modeled in c c code can be quickly allows floating point algorithms to be quickly specified in c c code and optimized and outputs the final design with. Large enough for product localparam SF 20 - 40. Here is the general method maybe there is a more clever or mathematical way.

One multiplies two matrices or a matrix with a scalar or a matrix with a vector. Floating Point Matrix Multiplication Verilog Code AN EFFICIENT IEEE 754 COMPLIANT FPU USING VERILOG April 24th 2019 - AN EFFICIENT IEEE 754 COMPLIANT FPU USING VERILOG 2012 Page 5 ABSTRACT A floating point unit FPU colloquially is a math coprocessor which is a part of a computer system specially designed to carry out operations on floating. We have implemented complex floating point numbers in Verilog HDL.

Define a float syntax. You must limit the range of var 30 to 09. Assume resulting exponent c ab.

We have to use multiplication with two floating points binary but it doesnt work 100 perfectly. If m does not have a single 1 left of radix point then adjust radix point. 0 a b c.

Iterative Matrix Multiplication x 0 n-1 x 1 G u n-1 x. Of course only integer can be supported in Verilog but we do have some method that can create and compute float numbers. Code in C programming language and generates highly efficient synthesizable Verilog or VHDL code for the FPGA.

Call this result m. Floating Point Matrix Multiplication Verilog Code Author. Like 8b0101_1001 equals 59 in DEC.

Floating Point Matrix Multiplication Verilog Code Author. The SpMxV is implemented in Verilog HDL. L3for int id 0.

The C code of the function to be optimized is as follows. Template void mmult_hwT ADIMDIM T BDIMDIM T CDIMDIM matrix multiplication of a AB matrix L1for int ia 0. After multiplying these two matrixes the result is written to another matrix which is BRAM.

The input is represented with single precision floating point representation in IEEE 754 format. Floating Point Matrix Multiplication Verilog Code. The first numbers before the comma are m 3116 and the numbers after comma m 150 so we have like.

Let a be the exponent of x and b be the exponent of y. Full Verilog code for the matrix multiplication is presented. Floating Point Matrix Multiplication Verilog Code Keywords.

M 3116 1000000000000000. M 150 1000000000000000. This application note explains how to design a floating-point matrix inversion module in the C.

Reg signed 15. Two fixed point matrixes A and B are BRAMs created by Xilinx Core Generator. Key WordsFPGA SPARSESimple Dual Port RAM MAC Floating PointCRS.

24 Pilchard Design Files - C Codes 25 Pilchard Host Interface 3 Floating-Point Number and Operations 31 Floating-Point Representations 32 Floating-Point Multiplication 33 Floating-Point Addition 4 Design and Implementation 41 Pilchard Design Flow 42 Matrix-Vector multiplication. I read this code on some book about floating point multiplication but the code missing one situation that one operand is zero so i try to add this portion but no response in output i dont know why please help me to understand that. Gauss-Jordan algorithm is performed on the floating point numbers 4 complex floating point numbers.

The size of the matrix is defined in the C header file and can be easily. Multiplying an mxn matrix is not possible because the information about the second argument a matrix a vector or a scalar is missing. Suppose that we have reg var 70 we can assume var 74 is the integer part and var 30 is the decimal part.

We have a Req m 310. It can be adjusted after the next step. The organization of the thesis is as follows.

Code running on Pentium4 processor. Q44 scaling factor is 2-4 initial begin display Fixed Point Examples from projectfio. Take the resulting number and multiply by 2-n where n is the number of iterations it took to get there.

The design is targeted on XC2VP70-7 Xilinx FPGA and met the operating frequency of 205MHz. Sparse Matrix-Vector multiplication SpMxVyAx is. The following module demonstrates all the calculations we performed above.

Anyway for any digital desig. We have a problem with Verilog. Ia L2for int ib 0.

Id sum Aiaid Bidib. Reg signed 7. The testbench code reads the content of the output matrix and writes to a resultdat file to check the result.

Multiply mantissa of x to mantissa of y. You cant use a point in Verilog binary literals but you can use an underscore.

Verilog Code On 8 X 8 Wallace Tree Multiplier Electronic Design Areas Of Computer Science

11366 Pdfs Review Articles In Verilog Hdl

Systolic Matrix Multiplier Digital System Design

Verilog Code For Multiplier Using Carry Look Ahead Adders Fpga4student Com

Pin On Fpga Projects Using Verilog Vhdl Fpga4student Com

Fpga Implementation Step By Step Digital System Design

Universal Shift Registes Verilog Code Code Example

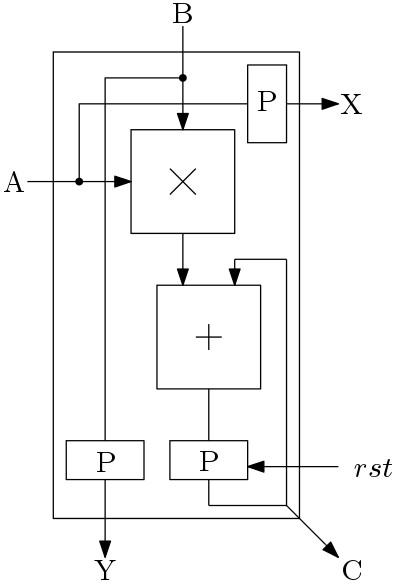

Sequential Multiplier Digital System Design

Sequential Multiplier Digital System Design

Normaliation Of Floating Point Multiplication Using Verilog Hdl Youtube

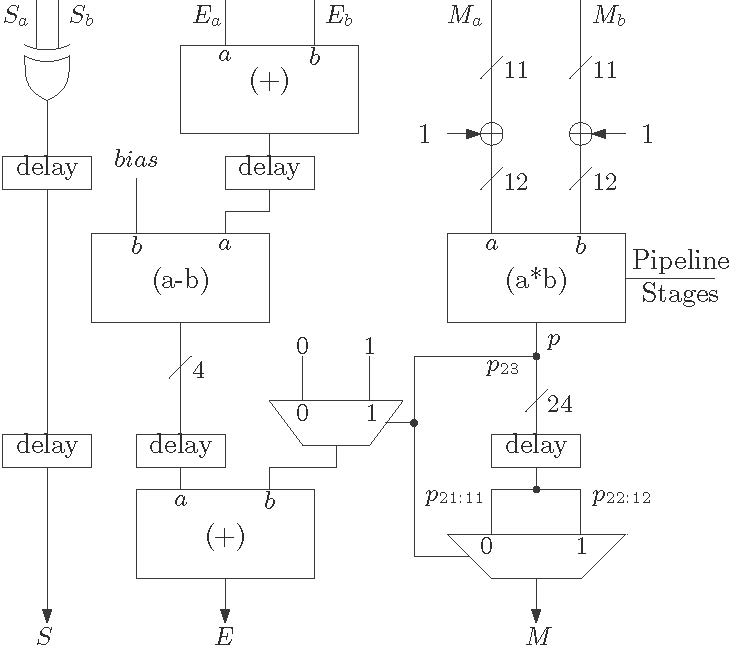

Floating Point Multiplication Digital System Design

Design Of 16 Bit Floating Point Fused Multiply Add Using Verilog Hdl Youtube

What Is The Verilog Code For Floating Point Multiplier Quora

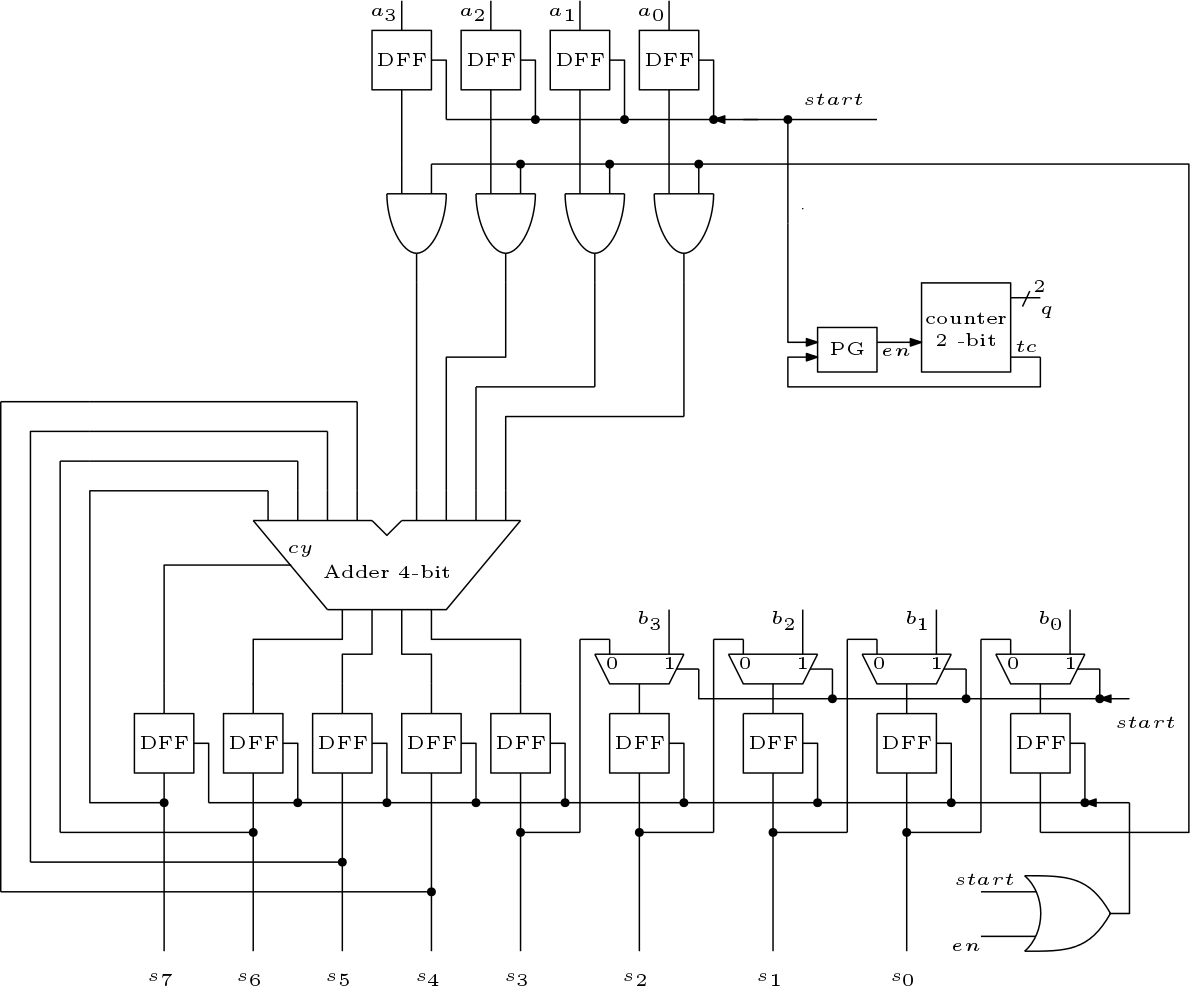

Fixed Point Matrix Multiplication In Verilog Full Code Tutorials Fpga4student Com

How To Implement A Shift Add Multiplier Using A Verilog Code Quora

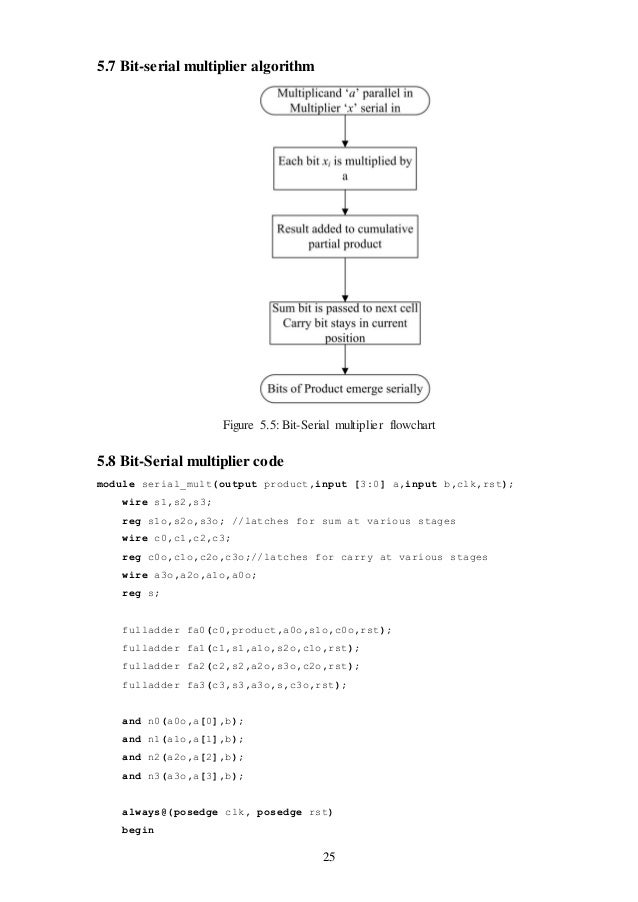

Bit Serial Multiplier Using Verilog

Pin On Verilog Code For Divider

Pin On Fpga Projects Using Verilog Vhdl Fpga4student Com

Verilog Code For D Flip Flop Fpga4student Com